据外媒Tomshardware当地时间27日报道,台积电日前在2023年IEEE国际电子元件会议(IEDM)上,发布进军至1nm制程的产品规划蓝图。

图片来源:Tomshardware

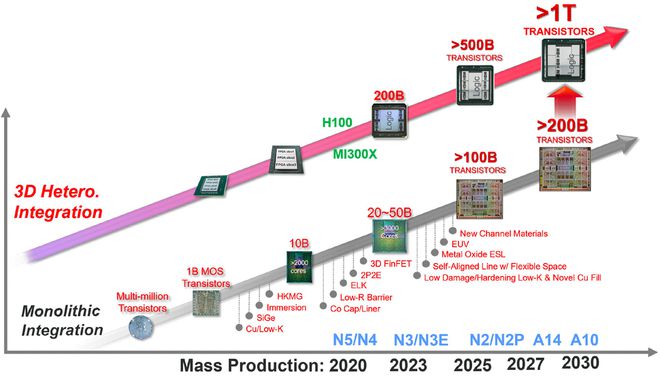

根据规划,台积电将并行推动3D封装和单芯片封装的技术路径的发展。预计在2025年,台积电将完成N2和N2P节点,使得采用3D封装的芯片晶体管数量超过5000亿个,而采用传统封装技术的芯片晶体管数量超过1000亿个。

然后,台积电计划在2027年达到A14节点,并在2030年达到A10节点,即1nm制程芯片。届时,采用台积电3D封装技术的芯片晶体管数量将超过1万亿个,而采用传统封装技术的芯片晶体管数量将超过2000亿个。

相比之下,采用4nm制程和传统芯片封装路径的GH100只有800亿个晶体管。

然而,值得注意的是,由于晶体管密度的提升越来越接近其物理极限,台积电近期提升制程水平的步伐正在遇到重大阻碍。

2023年6月27日,台积电在年度股东大会上宣布,其最新的3nm制程工艺芯片的良品率已经达到90%。但是,根据一些的未经证实的消息显示,台积电3nm制程芯片的良品率实际上只有50-55%,远低于其官方宣布的数字。

同期,苹果公司与台积电签署的对赌协议也侧面反映出台积电最新制程芯片良品率低于预期。根据对赌协议,未来一年台积电3nm制程芯片产能为苹果专用,但是如果生产的芯片中有不良的废片,苹果将不再按业界惯例为废片买单。这加重了外界对于台积电最新制程芯片良品率的怀疑。

此外,台积电的盈利能力下降也引起了外界对其未来发展的关注。据《华尔街日报》中文版报道,受智能手机和高速计算需求减弱的影响,台积电今年一季度的净利润同比增长2.1%,但二季度和三季度的净利润分别同比下降了23%和25%,营收和利润率都受到了影响。

在台积电发展速度放缓的同时,其在半导体代工领域的竞争对手,如三星等公司,并未放弃追赶台积电在先进制程领域的步伐。今年六月,三星代工公布了其最新的工艺技术发展路线图,计划在2025年推出2纳米制程的SF2工艺,在2027年推出1.4纳米制程的SF1.4工艺。一旦计划实现,三星有可能在与台积电相似的时间节点上实现类似的工艺水平。

本文系观察者网独家稿件,未经授权,不得转载。